Magic System

The Magic System is enabled when data is written to a memory location between 0 to 16K ($0–$3FFF), aka Magic Memory. Since this memory range is occupied by system ROM and cartridge ROM, respectively, data cannot be written to this area. Instead, a modified form of the data is actually written to memory location X + 16K. The Magic function generator uses a pair of registers, MAGIC ($C) and XPAND ($19), to perform the requested transformations.

Magic Register

The Magic Register (output port $C) byte determines how the data is modified. Each bit flags a specific data transformation. The purpose of each Magic Register bit is shown below:

| Bit | Function | Description |

|---|---|---|

| 0 | LSB of shift amount | Shift pixel data 0, 1, 2, or 3 pixels right before drawing |

| 1 | MSB of shift amount | |

| 2 | Rotate | Not supported on the Bally Arcade |

| 3 | Expand | Convert 1bpp data to 2bpp |

| 4 | OR | Draw in OR mode |

| 5 | XOR | Draw in XOR mode |

| 6 | Flop | Mirror pixel data |

| 7 | Unused | Must remain 0 |

The order in which magic functions are performed is as follows:

- Expansion

Rotationor Shift- Flop

- OR or XOR

As many as four functions can be used at any one time, and any function can be bypassed. OR and XOR cannot be done at the same time.

Rotation is not supported on the Bally Arcade. For more details, consult the Nutting Manual pp. 98–99.

Expander

The expander expands the 8-bit data bus into 8 pixels (i.e., 16 bits). It expands a 0 on the data bus into a 2-bit pixel and 1 into another 2-bit pixel. Thus, two-color patterns can be stored in ROM in half the normal memory space.

During each memory write instruction using the expander, either the upper half or the lower half of the data bus is expanded. The half used is determined by the expand flip-flop. The flip-flop is reset by an output to the magic register and is toggled after each Magic Memory write. The upper half of the data bus is expanded when the flip-flop is 0, and the lower half when the flip-flop is 1.

The expand register (output port $19) determines the pixel values into which the data bus will be expanded. A 0 on the data bus will be expanded into the pixel defined by bits 0 and 1 of the expand register. A 1 on the data bus will be expanded into the pixel defined by bits 2 and 3 of the expand register.

The pixels generated by bit 0 or 4 of the data bus will be the least significant pixel of the expanded byte. The most significant pixel will come from bit 3 or 7.

| XPAND Register Bit | Controls |

|---|---|

| 0 | Bits 0–1 define the color for 0 bits in the expanded pixel pattern |

| 1 | 00 = color 0, 01 = color 1, 10 = color 2, 11 = color 3 |

| 2 | Bits 2–3 define the color for 1 bits in the expanded pixel pattern |

| 3 | 00 = color 0, 01 = color 1, 10 = color 2, 11 = color 3 |

| 4–7 | Not used |

Example

LD A, 00001100B ; XPAND COLORS (11 AND 00) OUT (XPAND), A ; LOAD THE XPAND PORT . . . ; PATTERN DEFINITION PATTERN: DB 10000000B ; SMALL TRIANGLE POINTING RIGHT DB 11000000B ; 0 BITS WILL USE COLOR 0 DB 11100000B ; 1 BITS WILL USE COLOR 3 DB 11000000B DB 10000000B

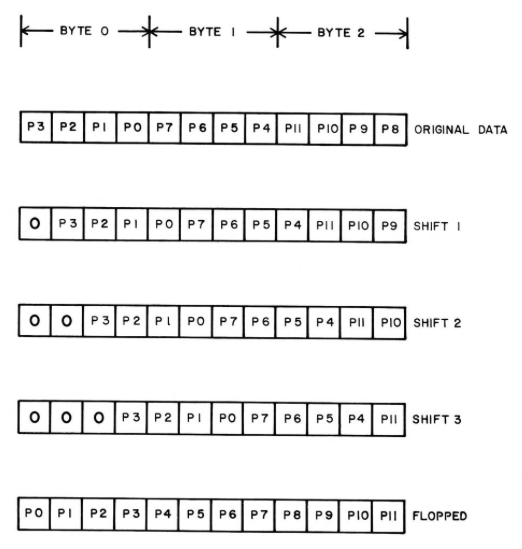

Shift and Flop

The shifter and flopper operate on pixels rather than bits. Each byte contains four pixels, each of which has one of four values. The four pixels are referred to as P0, P1, P2, and P3. P0 is composed of the first two bits of the byte.

Shifter

The shifter shifts data 0, 1, 2, or 3 pixels to the right. Bits 0 and 1 of the magic register determine the shift amount. The pixels shifted out of one byte are shifted into the next byte. 0's are shifted into the first byte of a sequence.

The shifter assumes the first byte of a sequence is the first magic memory write after an output to the magic register. Each sequence must be initialized by an output to the magic register, and data cannot be sent to the magic register in the middle of a sequence.

Flopper

The output of the flopper is a mirror image of its input. Pixel 0 and 3 exchange values, as do pixels 1 and 2.

The diagram below shows examples of shifting and flopping.

OR and XOR

These functions operate on a byte as 8 bits rather than four pixels. When the OR function writes data to RAM, the input to the OR circuit is ORed with the contents of the RAM location being accessed. The result is then written in RAM.

The XOR function operates in the same way, except that the data is XORed instead of ORed.

Intercept Register (Collision Detection)

Software reads the intercept register (input port $8) to determine if an intercept occurred on an OR or XOR write. An intercept is defined as the writing of a non-zero pixel (i.e., 01B, 10B, or 11B) location that previously contained a non-zero pixel.

A bit corresponding to the pixel position in the intercept register will be written to logical 1. Bits 0–3 give the intercept information for all OR or XOR writes since the last input from the intercept register. An input from the intercept register resets these bits. A bit is set to 1 if an intercept occurs in the appropriate position and will not be reset until after the next intercept register input.

| Bit | Meaning |

|---|---|

| 0 | Intercept in pixel 3 in an OR or XOR write since last reset |

| 1 | Intercept in pixel 2 in an OR or XOR write since last reset |

| 2 | Intercept in pixel 1 in an OR or XOR write since last reset |

| 3 | Intercept in pixel 0 in an OR or XOR write since last reset |

| 4 | Intercept in pixel 3 in last OR or XOR write |

| 5 | Intercept in pixel 2 in last OR or XOR write |

| 6 | Intercept in pixel 1 in last OR or XOR write |

| 7 | Intercept in pixel 0 in last OR or XOR write |

From A Description of the Bally Professional Arcade Video Hardware, p. 24:

“The Intercept register contains several flag bits which save the result of previous OR or XOR Magic Memory writes. If any of bits [3:0] are set, this indicates that the previous write to the corresponding pixel (bit[3] = pixel[3], etc.,) wrote a non-zero pixel with a non-zero value. Bits [3:0] track the last Magic memory write, while bits [7:4] track any write to the corresponding pixel (bit[7]=pixel[3],etc.,) since the last time the Intercept register was read. Thus, once any of bits [7:4] are set to logical 1, they will remain that way until the register is read, at which time these bits will be cleared to logical 0.”

Example: Space Invaders

The Space Invaders (proto) disassembly shows that invader bullets are written with XOR in the Magic Register of their VWRITR call, so collisions are checked as follows:

IN A,(INTST) ; inport =&(8) to CHECK INTercept STatus OR A RET Z ; done if No collision

Directly after the pattern write, intercept status is loaded in A, then A is ORed to see if any bits are set (indicating an intercept). If the OR result is 0, no collision occurs, and the collision check subroutine exits. (Football uses an identical check.)

[NM:94-100]

Reference: Magic Register Tutorial (1981) by Brett Bilbrey [PDF]